PA輸入端匹配直流電源電路的作用

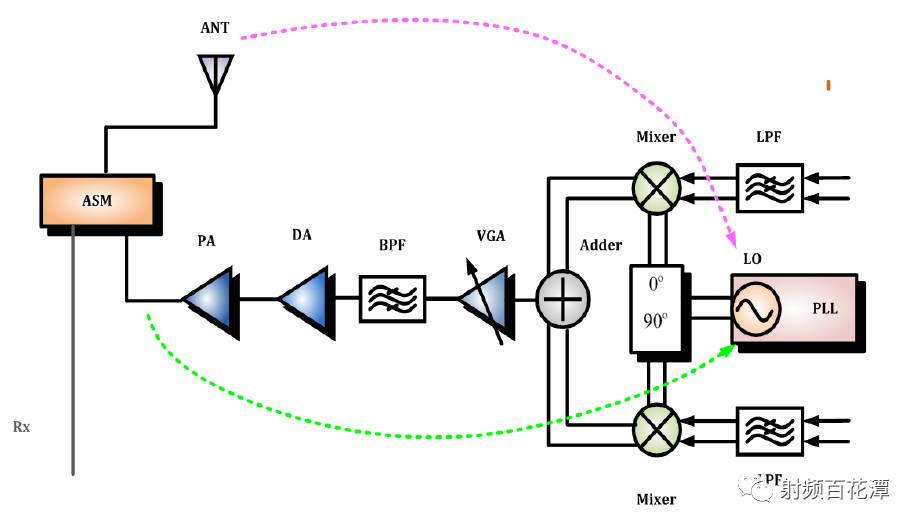

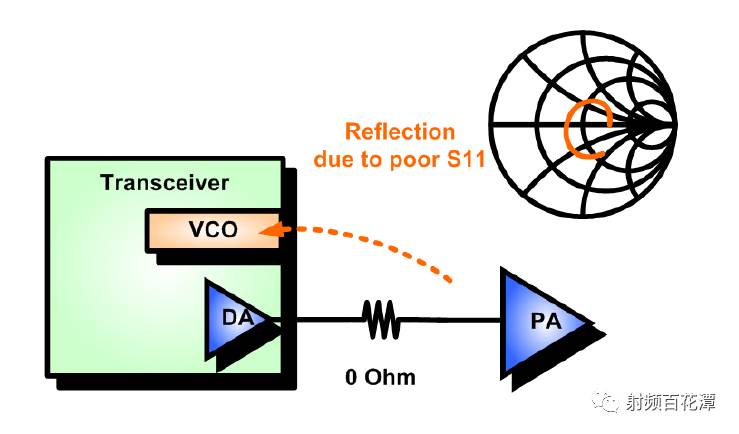

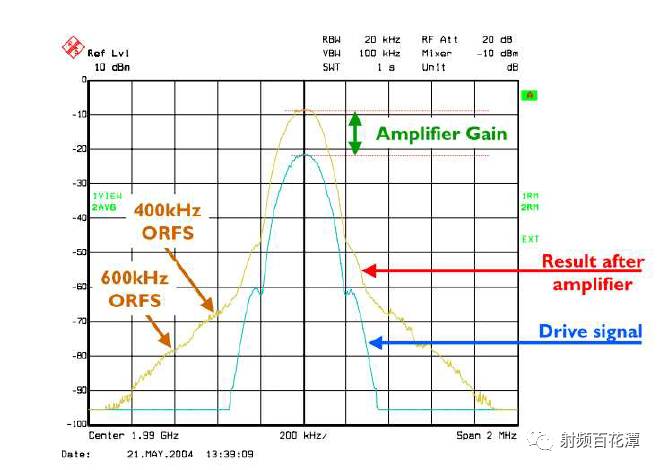

零中頻架構收發器,顧名思義,去除掉了中頻的零件,由于具備了低成本,低復雜度,以及高整合度,這使得零中頻架構的收發器,在手持裝置,越來越受歡迎。但連帶也有一些缺失,其中一項便是所謂的VCO Pulling,如下圖[1-3] :

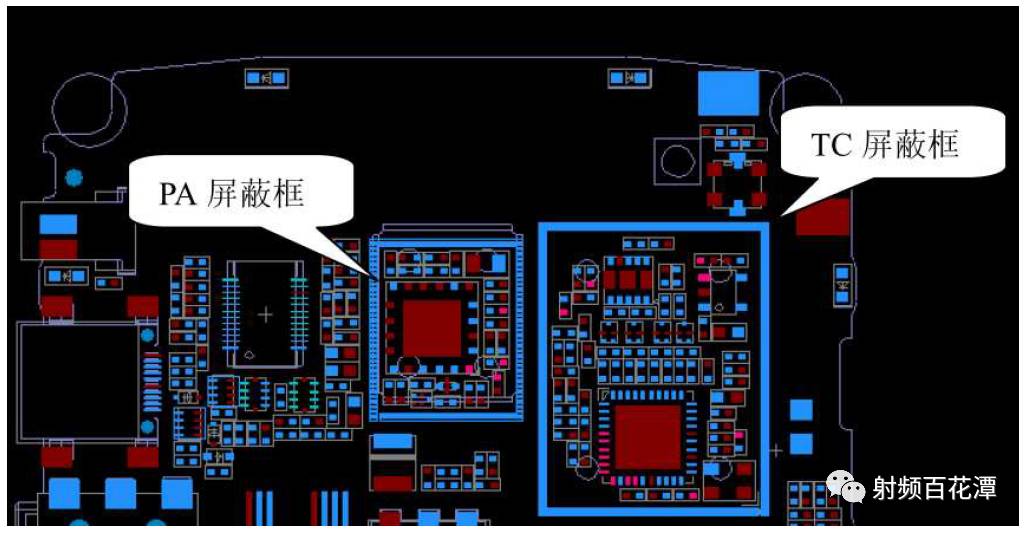

在零中頻架構中,因為主頻訊號的頻率與LO 相同,所以有可能會泄漏并造成干擾,而整個發射路徑中,最可能的泄漏來源為直流電源PA 輸出端與天線端,因為直流電源PA 輸出端的能量最強,因此會以傳導方式干擾,而天線端則是會直接以輻射方式干擾,使調變精確度下降,導致相位誤差,頻率誤差,以及EVM 都會有所劣化。因此不論是高通,或是MTK,都會建議收發器與直流電源PA要分別放在兩個獨立的屏蔽框里,也是為了避免VCO Pulling[1]。

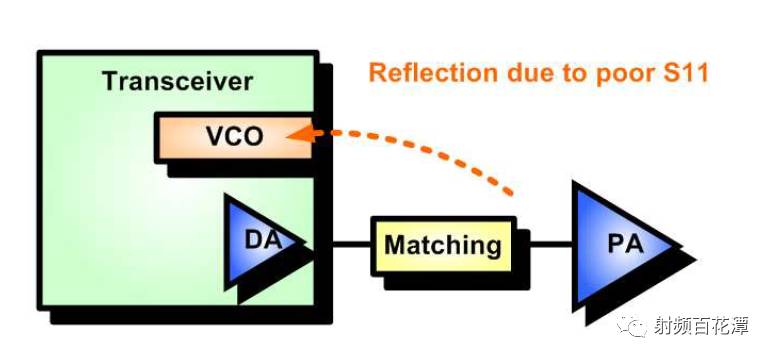

除此之外,直流電源PA 輸入端的匹配若沒調校好,會因反射而干擾VCO,導致調變精確度下降,如下圖 :

而直流電源PA 輸入端的匹配直流電源電路設計,其擺放位置需依平臺而定,例如若為MTK 的MT6252,則需靠近收發器,但若為高通的WTR1605L,則需靠近直流電源PA。

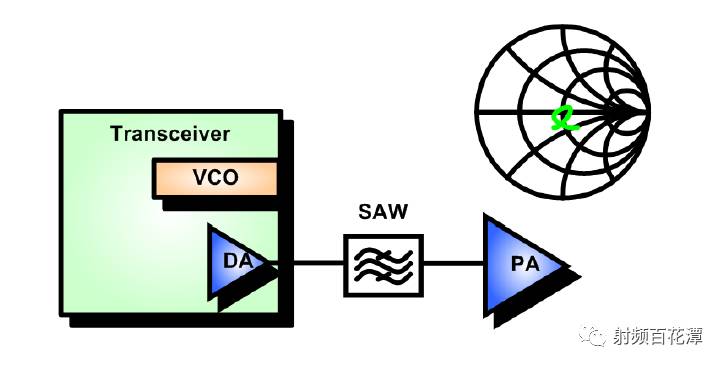

有時會遇到的問題是,將直流電源PA 輸入端的SAW Filter 拔掉,其相位誤差與EVM 會變差,此時可能有人會認為是SAW Filter 的關系,但這是個誤解,因為相位誤差與EVM,都是帶內噪聲,而SAW Filter 是用來抑制帶外噪聲,換言之,SAW Filter無法改善相位誤差與EVM,相反地,若SAW Filter 的Group Delay 過大,會導致信號有所失真,進而劣化EVM。

因此合理的解釋,便是VCO Pulling,當直流電源PA 輸入端放SAW Filter,此時收發器看出去的S11 很好,不會有訊號反射。

但是當直流電源PA 輸入端的SAW Filter 拔掉時,其發射訊號由于Layout 走線阻抗關系,導致收發器看出去的S11 不好,訊號反射打到VCO,使得調變精確度下降,其相位誤差與EVM 變差。故此時應針對直流電源PA 輸入端的Matching 再作微調,以減少反射[3]。

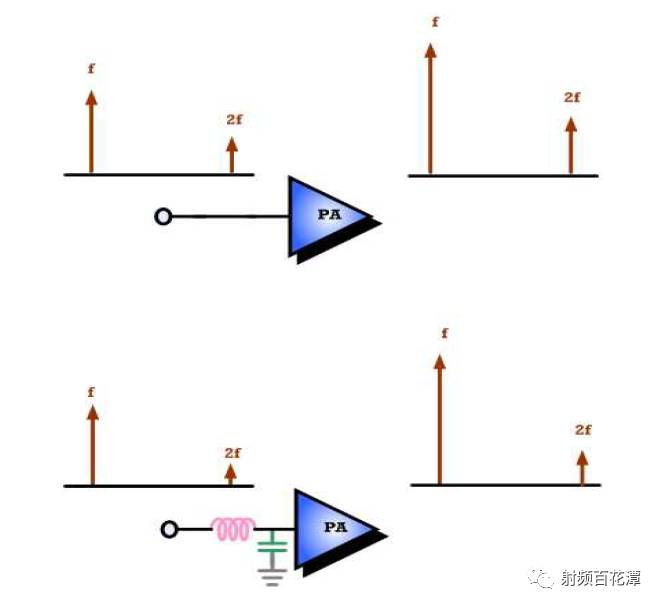

另外,由[4-6]可知,當RF 訊號的直流電源諧波過大時,可在直流電源PA 輸入端,設計LC 低通直流電源濾波器,先抑制直流電源PA 輸入端的直流電源諧波,避免因直流電源PA 的非線性效應,而使其更加惡化。

特別注意的是,不可將LC 低通直流電源濾波器,設計在直流電源PA 輸出端,因為會動到Load-pull。

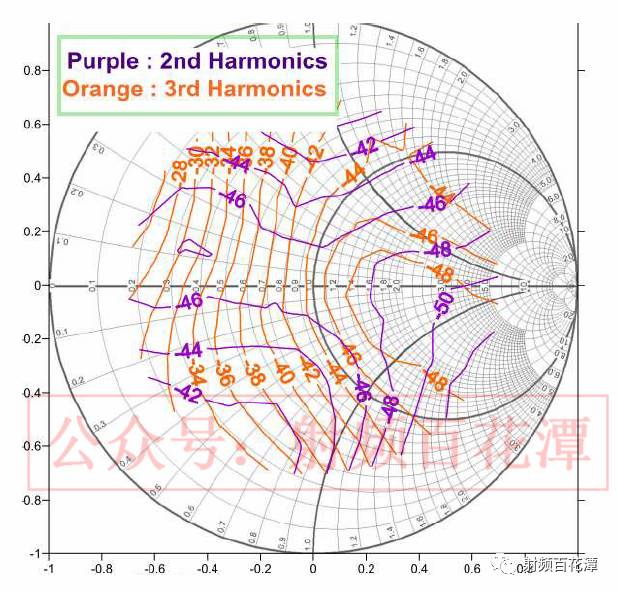

由上圖可知,不同的Load-pull,會有不同直流電源諧波值,第二象限是高直流電源諧波區,若該LC 低通直流電源濾波器,使Load-pull 跑到第二象限,進而導致直流電源諧波值變大,那么該直流電源濾波器抑制直流電源諧波的能力,便大打折扣。

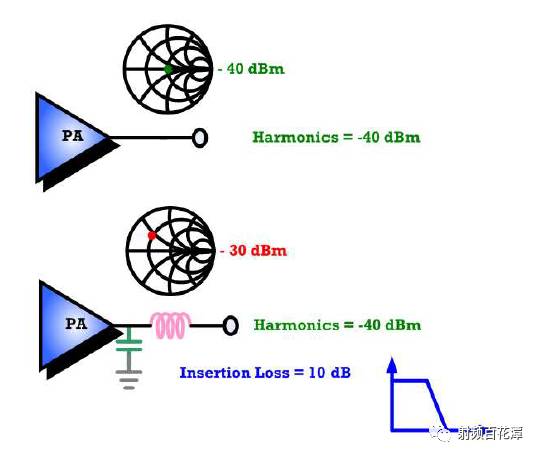

如上圖,假設該直流電源濾波器,其直流電源諧波的Insertion Loss 為10 dB,但因更動了Load-pull,使其直流電源諧波增加了10 dB,那么最終直流電源諧波會因其抵消結果,而并未所有抑制,故若將LC 低通直流電源濾波器,設計在直流電源PA 輸出端,那么該直流電源濾波器抑制直流電源諧波的能力,便大打折扣,即便最終直流電源諧波仍獲得改善,也會因Load-pull 更動,而導致其他發射端的性能都劣化[4-6]。

而由[1-2]可知,直流電源PA 的輸入端,其實也是DA(Driver Amplifier)的Load-pull :

因此這部分的匹配若沒調校好,會使DA 的線性度不夠,導致在直流電源PA 輸入端,開關頻譜已偏高的情況發生,再加上直流電源PA 是主要的非線性貢獻者,如此便會導致直流電源PA輸出端的開關頻譜更差。

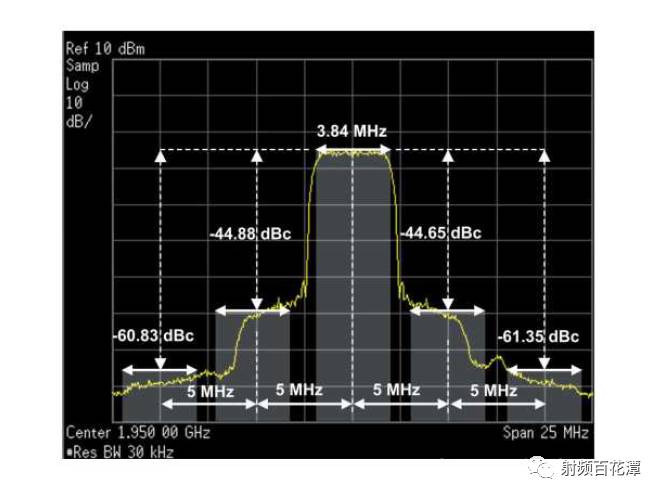

當然WCDMA 的ACLR,也是一樣道理,因此直流電源PA 輸入端的ACLR 不能太差,否則直流電源PA 輸出端的ACLR,肯定只會更差,而一線品牌大廠,其正負5MHz 的ACLR,都要求至少-40 dBc,

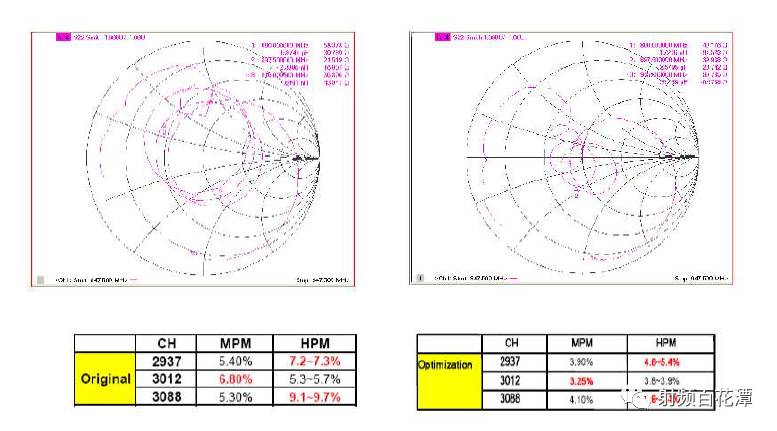

所以直流電源PA 輸入端,其正負5MHz 的ACLR 至少要-50 dBc。另外EVM 也是一樣道理,由下圖可知,當直流電源PA 輸入端的Matching 調校為較收斂的狀況時,其EVM 也跟著改善[2]。

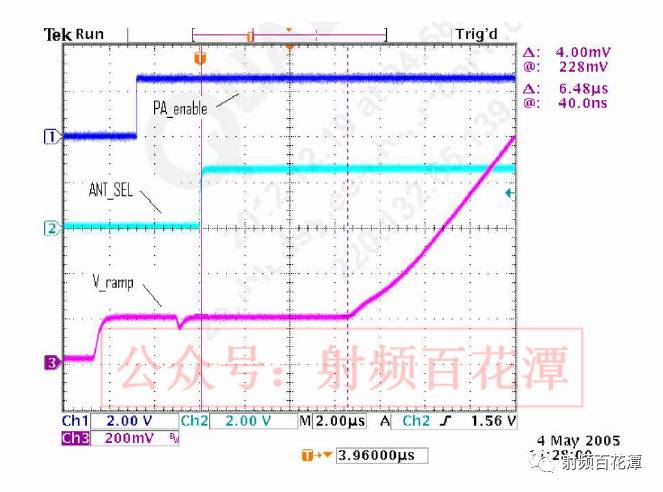

由于直流電源PA 的輸入功率范圍一向很廣,以RFMD 的RF3225 為例,其輸入功率范圍為0 dBm ~ 6 dBm,這表示收發器的輸出功率,即便扣掉Mismatch Loss 與Insertion Loss,仍符合直流電源PA 的輸入功率范圍,因此一般而言,較少調校此處的匹配,通常都是要debug 時,才會調校此處。而由以上可以看出,若直流電源PA 輸入端走線阻抗控制做得夠好,有收斂在50歐姆附近,理論上拿掉 是不至于出太大問題。當然,直流電源PA 輸入端Matching 拿掉,就無法兜低通直流電源濾波器,來解傳導雜散,不過若是高通平臺。還可以靠調NV 的方式來解。下圖是直流電源PA_Enable、ANT_SEL、V_ramp 三條曲線[1]。

這三條曲線,對于直流電源諧波以及開關頻譜,都會有影響,建議直流電源PA_Enable 比V_ramp早開啟,而且最好能早一段時間。而Ant_sel 可以比直流電源PA_en 早開啟,也可以比直流電源PA_en晚開啟,看怎樣的NV 值 其直流電源諧波以及開關頻譜會最低。

前面提到,若直流電源PA 輸入端走線阻抗控制做得夠好,有收斂在50歐姆附近,理論上其直流電源PA 輸入端的Matching 可拿掉。而若直流電源PA 沒有內建DC Block,則直流電源PA 輸入端需擺放串聯電容。然而,由[7-8]可知,串聯電容會使阻抗有所偏移,破壞原本已經控制好的阻抗。那這該如何處理呢 ?

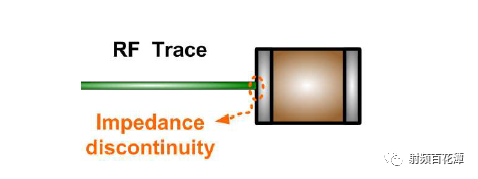

上式是容抗的公式,由上式可知,當電容值極大時,其阻抗會近乎于零。而作阻抗匹配前,要先將落地組件拔除,且串聯零歐姆電阻,來得知走線的原始阻抗[8],因此可知串聯零歐姆電阻,并不會改變原始阻抗。而前述已知,電容值極大時,其阻抗會近乎于零,相當于零歐姆電阻,故可知若想抵擋直流訊號,但又不想使阻抗有所偏移時,可以擺放大電容,來同時兼具這兩種需求。然而這邊所謂的大電容,并不需要到uF 等級,因為uF 等級的電容,至少都是0603 的尺寸,若擺放在走線,不僅占空間,同時也會因寬度與走線差異過大,產生很大的阻抗不連續,以至于Mismatch Loss 增加,如下圖:

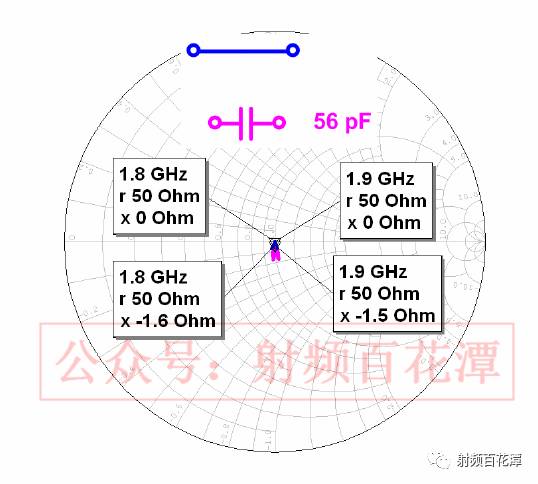

因此pF 等級的電容即可,以DCS 1800/PCS 1900 為例,由下圖可知,串聯56 pF的電容,其阻抗幾乎不變。

由前述我們可總結,直流電源PA 輸入端匹配直流電源電路設計的作用,主要是用來debug 的 :

1. 頻率誤差/相位誤差, EVM,調制頻譜 => 減少反射,避免VCO Pulling。

2. 傳導雜散 => 設計低通直流電源濾波器,減少直流電源諧波。

3. ACLR,開關頻譜 => 提升DA 線性度。

若阻抗控制有做好,原則上可以拿掉,以節省空間。但建議初始設計時,還是先擺放,以防萬一,確認其發射性能皆無大礙時,下一版直流電源PCB 設計再將其拿掉。

- 上一篇:蓄電池:鋰離子電池及其電池管理系統分析 2017/6/14

- 下一篇:MCU外接晶體及振蕩電路分析 2017/6/14